산업 생산 라인에서 제조된 N형 PSPC(폴리실리콘 후면 부동태화 접촉) 셀의 효율은 지난 3년 동안 20.7%에서 23.6% 이상으로 증가했습니다. 급속한 효율 상승은 붕소 방출체와 얇은 n+ 폴리실리콘 층 모두에 접촉할 수 있는 금속화 페이스트에 의해 강력하게 뒷받침됩니다. 산업계에서 일반적으로 사용되는 폴리실리콘층의 두께는 160~200nm 정도이다. 비용을 절감하고 성능을 향상시키기 위해 태양전지 제조업체는 폴리실리콘 층 두께를 100nm 또는 심지어 50nm로 줄이고 싶어합니다. 기존의 금속화 슬러리는 소결 과정에서 더 얇은 다결정 층을 통해 연소되고 부동태화를 방해하기가 매우 쉽기 때문에 더 얇은 다결정 층에 적합한 슬러리를 개발하는 것은 큰 어려움을 안겨줍니다.

이와 관련하여 연구진은 SiNx 및 폴리실리콘 박막의 에칭에 대한 은 페이스트 화학의 영향을 자세히 연구했으며, 낮은 소결 온도에서 양호한 접촉을 유지하면서 개방 압력을 높일 수 있는 새로운 금속화 페이스트 제제를 개발했습니다. 이 새로운 PSPC용 은 페이스트는 50°C의 소결 창에서 일관된 접촉 저항을 가지며 50⁰C의 더 낮은 소결 온도에서 더 높은 충진율을 달성하여 0.2%의 효율 이득을 얻습니다. PSPC 금속화 슬러리의 이러한 개선은 미래 태양전지의 더 얇은 다층 두께와 일치할 수 있습니다.

N형 TOPCon 태양전지 뒷면의 더 얇은 폴리실리콘 층 방향에 대해 다음 두 가지 측면이 연구되고 탐구됩니다.

1. 침식에 대한 은 페이스트 화학의 영향

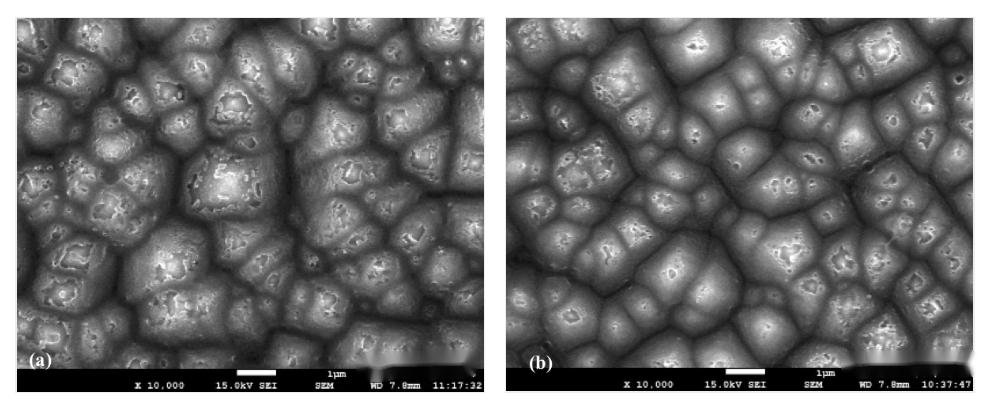

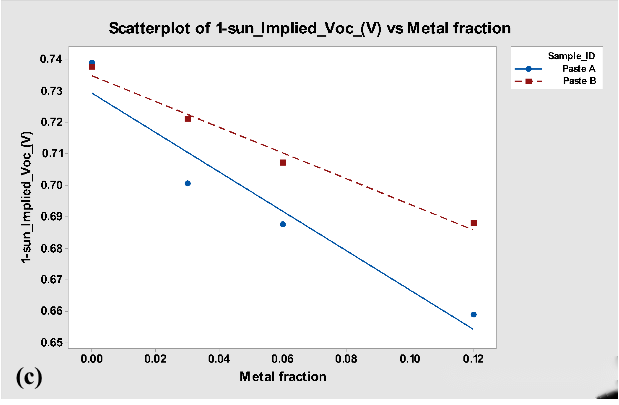

은 페이스트 A와 은 페이스트 B에는 점도와 공격성이 서로 다른 유리가 포함되어 있습니다. 두 가지 실버 페이스트 모두 표면 텍스처링 후 n형 실리콘 웨이퍼에 인쇄되며, 실리콘 웨이퍼 표면은 위에서 아래로 SiNx 층과 150nm 두께의 n+ 폴리실리콘 층을 갖습니다. 은 및 유리 층을 제거한 후 SEM 다이어그램에서 은 페이스트 A는 넓은 면적의 SiNx 및 다결정 층을 에칭하여 스웨이드를 매우 거칠게 만든 반면, 은 페이스트 B는 매우 작은 면적의 SiNx 및 다결정 층만 에칭한 것을 볼 수 있습니다. , 피라미드 꼭대기 근처에서는 약간의 효과만 나타납니다. 3%, 6% 및 12% 금속화 영역에 해당하는 은 페이스트 B를 인쇄하여 얻은 Voc는 은 페이스트 A의 Voc보다 높았으며, 이는 또한 은 페이스트 B가 더 온전한 폴리실리콘 보호층을 유지한다는 것을 보여주었습니다(그림 1 참조). 바닥층의 터널링 산화물은 손상되지 않았으며 이는 태양전지에 대한 부동태화 효과를 크게 보호했습니다.

그림 1: (a) 은 페이스트 A를 사용하여 은 및 유리 층을 제거한 후의 샘플 (b) 은 페이스트 B를 사용하여 은 및 유리 층을 제거한 후 샘플 (c) 은 페이스트 A 및 은 페이스트 B의 Voc 값 다양한 금속화 영역에 해당합니다.

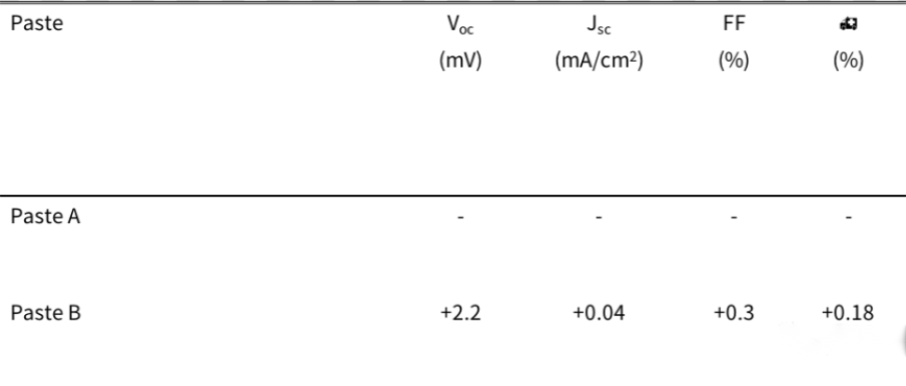

또한 은 페이스트 A와 은 페이스트 B는 150nm n+ 폴리실리콘 층을 갖춘 n형 PSPC 실리콘 웨이퍼의 전체 생산 라인에서 테스트되었습니다. 주사전자현미경은 덜 에칭된 은 페이스트 B가 2.2mV의 Voc 이득과 0.3%의 필러 인자 이득을 갖는 셀을 생성하여 0.18%의 절대 효율 향상을 가져온다는 것을 보여주었습니다(표 1 참조).

생산라인에서 두꺼운 160nm 폴리실리콘층을 적용한 TOPCon 태양전지의 슬러리 효율 비교

2 저온 소결에 적합한 새로운 무기 시스템

폴리실리콘 층을 얇게 만드는 것은 셀에 두 가지 이점을 제공합니다.

1. 증착 공정의 생산량을 늘려 비용을 절감합니다.

2. 폴리실리콘층의 기생 광 흡수를 줄여 광 이용 효율을 향상시킵니다.

얇은 두께의 폴리실리콘 층의 품질을 유지하려면 실리콘 웨이퍼를 낮은 온도에서 소결하는 것이 가장 좋습니다. 유리의 물리화학적 특성은 최적의 소결 온도 또는 은 페이스트 소결 창의 범위에 결정적인 역할을 합니다. 얇은 폴리실리콘 층 구조를 위해 연구진은 50⁰C의 넓은 소결 창에서 접촉 저항률이 일정할 수 있고 낮은 온도에서 전체 효율이 향상되는 특수 유리 시스템을 특별히 개발했습니다.

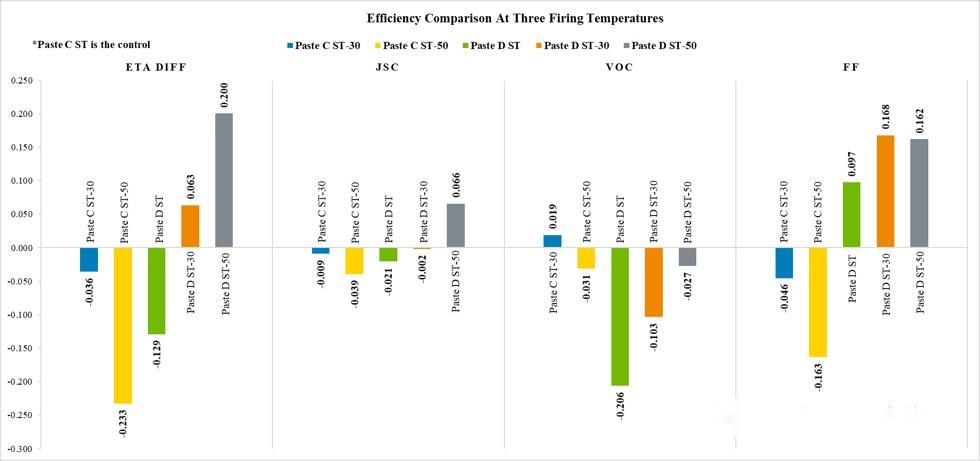

그림 2에 표시된 것처럼 은 페이스트 C가 기준 샘플이고 은 페이스트 D에 특별히 개발된 유리가 포함되어 있는 경우 FF의 급격한 감소로 인해 피크 소성 온도가 감소함에 따라 은 페이스트 C의 효율이 감소합니다. 반대로, Silver Paste D의 Voc, FF 및 효율은 증가하는 반면, 최고 소결 온도는 감소합니다. 표준 온도보다 50°C 낮은 은 페이스트 D는 표준 소결 온도의 기준 샘플 슬러리 C에 비해 0.2%의 효율 이득을 갖습니다.

그림 2: 표준 피크 온도인 30°C(ST-30), 50°C(ST-50) 및 표준 피크 온도(ST) 미만에서 소결된 실버 페이스트 C 및 D의 상대값.

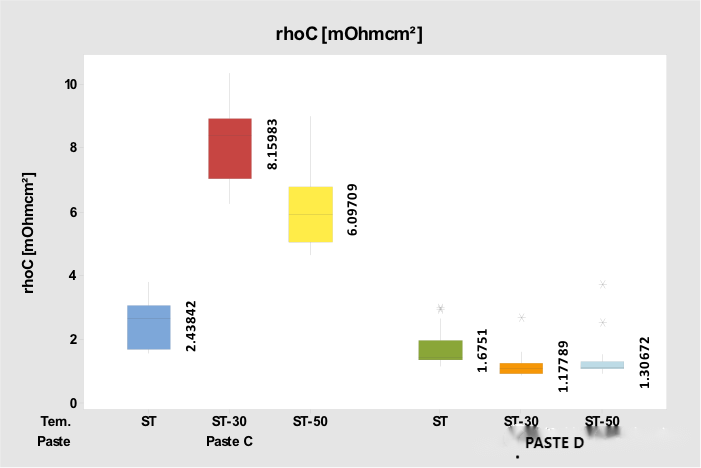

그림 3에 나타난 바와 같이, 실버 페이스트 C의 접촉 저항은 소성 온도가 감소함에 따라 크게 증가하는 반면, 은 페이스트 C의 접촉 저항은 증가한다.세 가지 소성 온도에서 은 페이스트 D는 1.1-1.7 mohm·cm2 범위에서 매우 안정적입니다.

그림 3: 표준 피크 온도 30°C(ST-30), 50°C(ST-50) 및 표준 피크 온도(ST) 미만에서 소결된 실버 페이스트 C 및 D의 접촉 저항률(Rhoc)

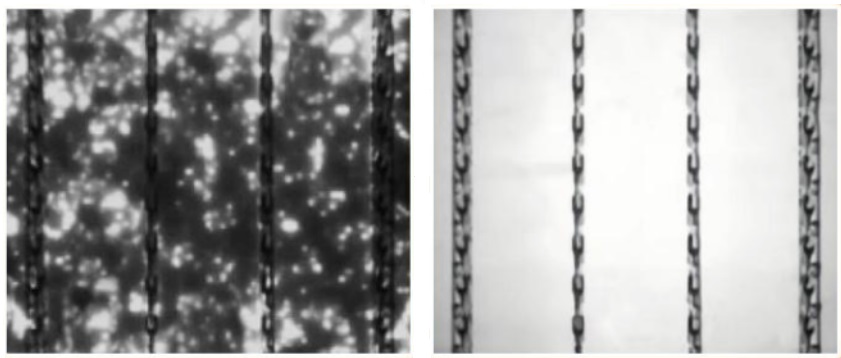

또한 후면 TOPCon 구조에는 SiNx, 폴리실리콘층 및 터널링 산화물 보호층 외에 AlOx 보호층이 있으며, 저온에서도 양호한 접촉을 형성할 수 있는 새로운 무기 시스템이 개발되었습니다(ST-50). 부동태화 효과를 최대한 유지하면서, 그림 4는 기준 슬러리 E 소결 EL 사진과 비교하여 특수 무기 설계 슬러리 F를 보여줍니다. 일반 슬러리가 EL 흑화와 접촉할 수 없는 경우 F 슬러리 EL은 밝음을 알 수 있습니다. 좋은 접촉이 형성됩니다.

그림 4: (a) E 슬러리 저온 소결 후 EL 사진 (b) F 슬러리 저온 소결 후 EL 사진

저온 소결 N형 TOPCon 후면 슬러리와 일치시키기 위해 전면 보로 팽창 실리콘 웨이퍼 접촉 슬러리도 개발되어 금속화로 인한 복합물을 최소화하는 동시에 다양한 제곱 저항 및 다양한 스웨이드와의 높은 접촉을 유지합니다. 실리콘 웨이퍼와 새로운 유기 시스템은 더 미세한 그리드 라인 인쇄와 호환되므로 셀의 전반적인 효율성이 최적화되고 향상됩니다.