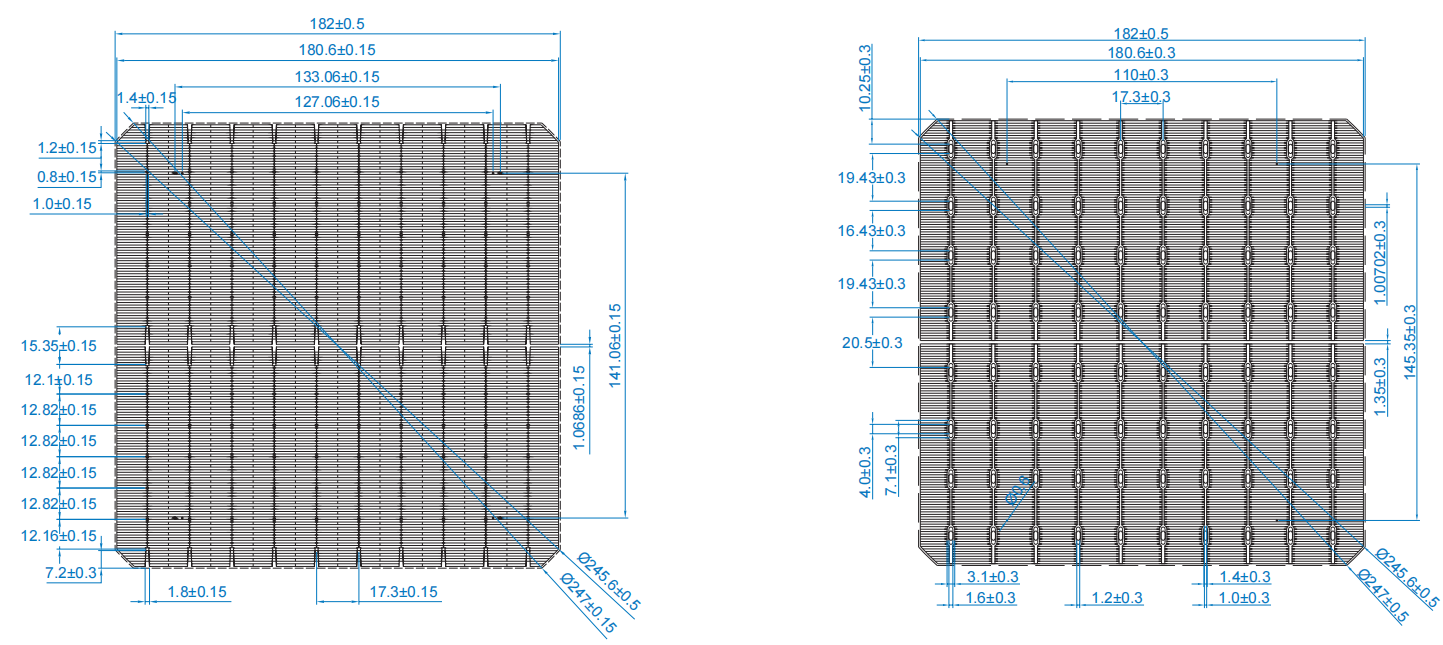

치수 :

182mmx182mm±0.5mm, Φ 247mm±0.5mm두께 :

175μm±17.5μm앞쪽 (-) :

10 busbars, 14 pads, 170 fingers, busbar width 1.2±0.3mm뒤로 (+) :

10 busbars, 8 pads, 180 fingers, busbar width 1.2±0.3mm

PERC 기술 도입

PERC는 부동태화 이미터 및 후면 접점 또는 부동화 이미터 및 후면 셀을 의미합니다.

기존 셀은 패널 제조업체가 전면 패널에서 전자 재결합을 방지하기 위해 전면 패시베이션 층을 배치하기 시작하면서 효율성이 급상승했습니다. 패널 후면에 닿는 전자의 수를 줄임으로써 효율성을 더욱 높일 수 있었습니다.

PERC 셀은 PV(광발전) 패널의 후면에 추가 캡핑 및 패시베이션 층을 배치하여 후면 재결합을 줄임으로써 한 단계 더 발전했습니다. 이러한 층은 또한 반사되지 않은 태양 복사로 인해 패널이 가열되는 것을 방지하는 데 도움이 됩니다. 패널은 더 낮은 온도에서 더 나은 성능을 발휘하므로 성능 향상에도 도움이 됩니다. PERC 셀은 비슷한 방식으로 작동하지만 몇 가지 주요 차이점이 있습니다.

음전하를 띤 n형 시트는 일반적으로 음전하를 유지하기 위해 외부 껍질에 인과 같은 추가 전자를 갖는 더 많은 원자를 포함합니다.

양의 p형 시트에는 추가 전자가 들어갈 수 있는 양으로 하전된 정공이 포함되어 있습니다. 이들은 일반적으로 붕소 또는 갈륨이며 주변의 실리콘과 결합하는 데 필요한 원자가 전자가 하나 부족합니다.

외부 전자를 잃은 원자(정공)는 자연적으로 여분의 원자가 전자를 가진 원자와 결합합니다. 이로 인해 결합에서 하나의 추가 전자가 남게 되고, 이는 방전되어 전기로 수집됩니다.

태양 에너지가 패널에 유입되면 양극 및 음극 실리콘 층이 자연스럽게 재균형을 이루고 공정이 다시 시작됩니다. 기본 아이디어는 동일하지만 PERC 셀에는 전자가 외부 세계로 손실되는 것을 방지하기 위해 몇 개의 추가 레이어가 있습니다.

엔지니어링 도면(mm)

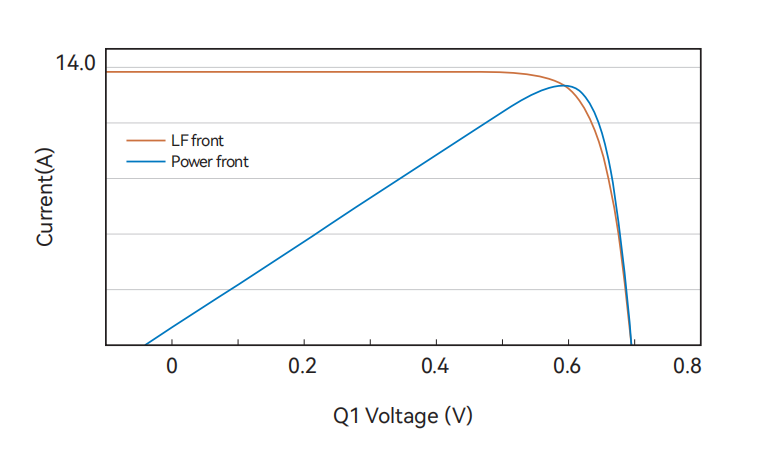

온도 계수 IV 곡선

Tk현재 | 0.07%/℃ |

TkPower | - 0.36%/℃ |

Tk전압 | - 0.36%/℃ |

앞쪽 전기적 성능 분포

능률 효율(%) | 최고 출력 파워 Pmpp(W) | 최대 전원 전압 Vmpp(V) | 최대 출력 포인트 전류 임프(A) | 개방회로 전압 VOC(V) | 짧은- 회로 현재의 ISC(A) |

>23.5 | 7.76 | 0.593 | 13.086 | 0.692 | 13.776 |

23.4~23.5 | 7.73 | 0.592 | 13.057 | 0.691 | 13.762 |

23.3~23.4 | 7.69 | 0.591 | 13.012 | 0.690 | 13.730 |

23.2~23.3 | 7.66 | 0.590 | 12.983 | 0.689 | 13.713 |

23.1~13.2 | 7.63 | 0.589 | 12.954 | 0.688 | 13.686 |

23.0~23.1 | 7.59 | 0.588 | 12.908 | 0.687 | 13.639 |

22.9~23.0 | 7.56 | 0.587 | 12.879 | 0.686 | 13.601 |

22.8~22.9 | 7.53 | 0.586 | 12.850 | 0.685 | 13.635 |

22.7~22.8 | 7.49 | 0.585 | 12.803 | 0.684 | 13.575 |

22.6~22.7 | 7.46 | 0.584 | 12.774 | 0.683 | 13.564 |

22.5~22.6 | 7.43 | 0.583 | 12.744 | 0.682 | 13.554 |

22.4~22.5 | 7.40 | 0.582 | 12.715 | 0.681 | 13.541 |

22.1~22.3 | 7.30 | 0.579 | 12.608 | 0.678 | 13.527 |

22.0~22.1 | 7.26 | 0.578 | 12.561 | 0.677 | 13.495 |

표준 테스트 조건:1000W/m², AM1.5G, 25℃. 위의 기술 매개변수는 기술적 변경이 가능하며 테스트. 이 데이터시트에 포함된 모든 데이터는 예고 없이 변경될 수 있습니다. | |||||